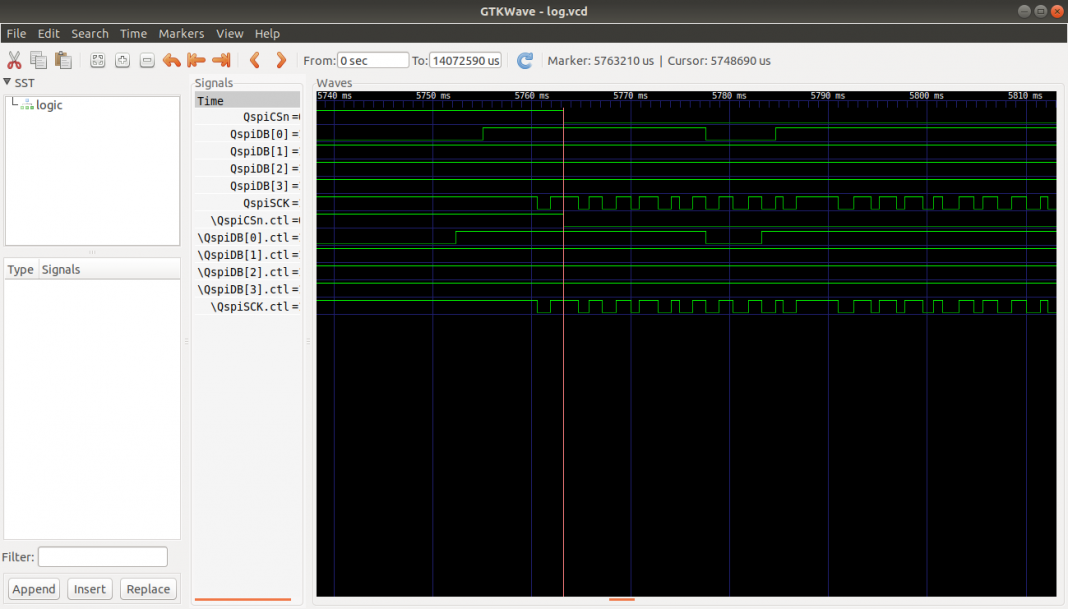

Paul Gardner-Stephen over at MEGA65 reports he’s getting closer to being able to communicate with the QSPI flash, so that he can have the MEGA65 update its own bitstreams in the field.

To recap the current situation:

1. Most of the signals to the flash are easy to connect to with the QSPI flash, except the clock, which is normally driven by the FPGA’s configuration logic.

2. The FPGA has a facility, the STARTUPE2 component, that allows the running bitstream to take control of this signal.

3. I have managed to achieve (2) in a test bitstream, as confirmed by my new JTAG boundary scan setup.

4. But I haven’t got it working for a real bitstream.

To read more about it check out Paul’s latest blog entry.